博文

降低芯片设计创新门槛——从互联网成功经验看开源芯片生态发展

||

降低芯片设计创新门槛

——从互联网成功经验看开源芯片生态发展

中国科学院计算技术研究所研究员 包云岗

2018年,中国企业遭遇芯片禁售令而陷入困境,中国半导体产业的现状再次引起各界广泛关注。如何尽快找出一条破解之道,在笔者看来,除了国家加大对卡脖子技术的重点扶持以正面应对之外,呼吁各界参与开源芯片行动,也不失为一条新的道路。

开源软件 助力中国互联网产业成功

2018年4月10日,脸书创始人马克·扎克伯格在参加美国国会听证会时,与阿拉斯加共和党参议员苏利文之间进行了这样一段对话:

苏利文:你不可能在中国成功,是吧?或者,无法在那里取得过去10年你所取得的成就。

扎克伯格:参议员,中国有很多强大的互联网公司。

苏利文:好吧,但你刚那个问题应该回答“是”。

显然,在扎克伯格看来,中国的互联网公司在国际上是具有竞争力的。中国占据世界十大互联网公司的四席,共享经济、移动支付也世界领先。

2016年美国移动支付金额为1120亿美元,而中国则达到了5.5万亿美元,是美国的50倍。2017年11月11日,阿里巴巴“双十一”成交额达到惊人的1682亿(约为260亿美元)。相比之下,美国黑色星期五(2017年11月24日)的网络销售成交额仅为50.3亿美元。根据阿里提供的数据,“双十一”零时5分22秒,支付宝的支付峰值达到每秒25.6万笔,其数据库处理峰值更是达到每秒4200万次操作,均刷新了世界纪录。相比之下,全球最大的清算组织VISA的交易峰值仅为1.4万笔/秒,也就是支付宝的二十分之一。

中国互联网公司的成功离不开背后强大的技术支持。它们普遍使用开源软件来构建其业务系统。开源软件,就是一种源代码可以自由获取并在遵循开源协议的规定下,进行自行修改而无需付费的计算机软件。

对于互联网企业而言,开源软件为它们节省大量的时间与成本。据统计,常用的开源软件已经构成了一个价值超过150亿美元的开源软件生态,一些开源软件如LAMP(Linux + Apache + MySQL + PHP)组合或MEAN(MongoDB + Express + AngularJS + Node.js)组合,已经成为互联网公司(尤其是初创公司)构建其业务的标配,让其可以更专注于业务创新上。

图1 价值上百亿美元的开源软件栈

(图片来源于Andreas Olofsson, Intelligent Design of Electronic Assets, 2017)

阿里前副总裁章文嵩博士就曾在一次演讲中提到,阿里因为使用开源软件而节省了大量成本。有了开源软件,当人们想创办摩拜这样的新公司,不再需要从零开始造“轮子”,而是可以在庞大的开源软件库中寻找到合适的模块并根据需要进行合适的修改。比如利用LAMP组合,3—5位开发人员就在几个月时间里快速搭建出一个业务原型。因此,开源软件很重要的意义在于大大降低了互联网创新的门槛。

另一方面,开源软件也可以让中国的互联网产业,在软件技术方面不再面临“卡脖子”问题,从而让中国的互联网企业能与硅谷几乎在同一起跑线上竞争,甚至在共享经济、移动支付等领域更具竞争力。当银行等传统企业还严重依赖于IOE(IBM的小型机、Oracle的数据库、EMC的存储)时,中国的互联网企业却已经用行动证明了“去IOE”的可行性,这一切都得益于中国互联网企业积极拥抱开源软件的实践。

资金高门槛 让后来者追赶无望

开源软件解决了中国互联网产业发展过程中的两大难题,一是降低了创新的门槛,二是摆脱了技术上的受制于人。而这两个难题却正是当前中国半导体产业所面临的困境。

芯片领域的创新门槛之高、投入之大是业内公认的。设计与制造一款芯片涉及到多个环节,包括EDA开发环境搭建、外围IP模块选型、芯片前端逻辑设计、后端物理设计、流片与封装测试等,每个环节都需要相当的资金与人力投入。

以28nm工艺研制一款SoC芯片为例,比较完整的EDA工具使用版权费便超过500万元,购买内存控制器、PCIe控制器等外围IP模块费用往往达到500—1000万元,流片费用根据芯片面积大小而定,但一般也会达到1000万元,封装相对便宜,大约需要50万左右。简单估算,研制这款芯片所需要的资金投入便已经超过2000万元。另一方面,芯片的研发往往需要数十位工程师,花上一年的时间来设计与验证,仅工资开销就需要上千万元。但是,芯片设计与验证时哪怕出现一个很小的错误,都有可能导致芯片最终无法工作。不光前期的投入打水漂,开发人员还不得不再花上千万元重新流片。

芯片领域的高门槛客观上严重阻碍了创新。在互联网领域,得益于开源软件,拥有创新想法的互联网初创公司,往往只需几百万元甚至几十万元,便可以在几个月时间里推出原型产品进行迭代优化。相比而言,芯片领域的初创公司却需要数千万的资金,而且迭代优化还要很长的时间周期,所以很难想象风险投资人愿意把钱砸给这类初创公司。

事实上,半导体、大规模集成电路发展的黄金期是上世纪六七十年代,当时芯片规模都很小、成本较低,却又具有很高的收益,吸引了美国、日本、中国台湾等大量优秀的人才投入到半导体领域创办公司,也吸引了大量资本投入到这个领域,但中国大陆错过了那个黄金时代。经过半个世纪的发展,少数发达国家和地区通过市场机制自然地形成了技术积累与产业优势,同时构建了极高的创新门槛,不仅让后来者追赶无望,也让芯片成为他们“卡别人脖子”的利器。

如今中国的半导体产业要想改变现状,已经很难完全靠初创企业与风险资本来追赶了,必须通过必要的产业政策来引导。笔者认为,借鉴中国互联网产业的成功经验,降低芯片设计的创新门槛是关键。

开源芯片 为设计创新插上翅膀

近期受到普遍关注的开放指令集RISC-V,从生态构建角度为开源芯片设计作出了积极的工作。RISC-V是由美国加州大学伯克利分校的Kreste Asanovic教授与图灵奖得主David Patterson教授带领团队设计的一套开放指令集。

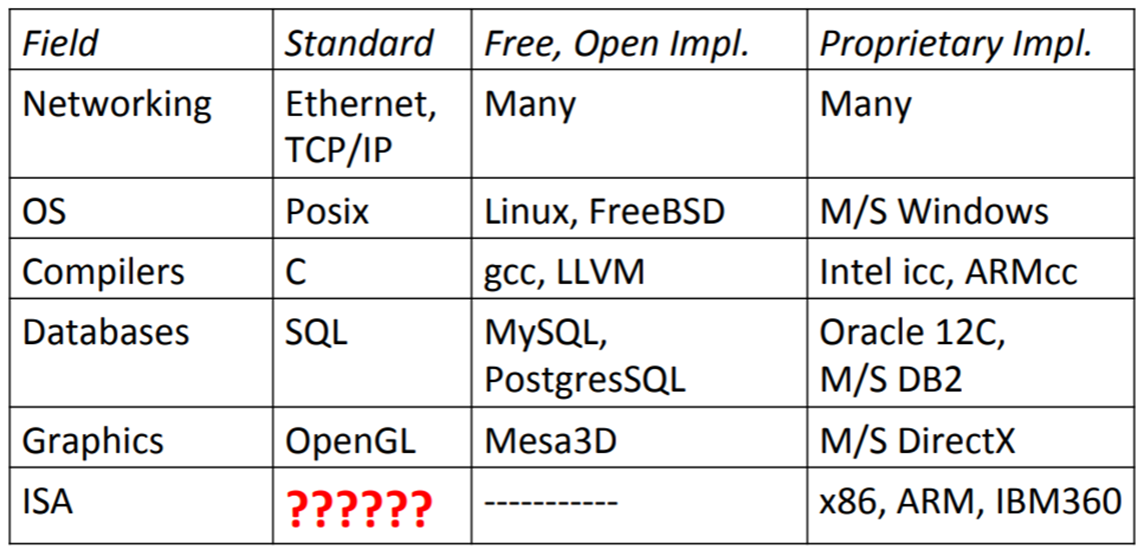

伯克利团队推出RISC-V,正是受到了开源软件的启发,但开源软件生态和处理器芯片生态的情况却大不相同。如表1所示,开源软件中的不同领域,都有一套开放的标准,在这套开放的标准之下,既有开放自由的实现,也有企业私有的实现。虽然总体上私有实现的效果更优,但开放自由的社区也非常活跃。然而,处理器芯片领域,从指令集到处理器实现全是Intel、ARM这样的私有企业掌控,甚至连开放的指令集标准都没有,更不用说开源的处理器芯片设计。

表1 开放软件和标准小结

(来源:Instruction Set Want to be Free, Krest Asanovic, David Patterson)

如果有一款开放自由的指令集,大家都可以用它来做任何事情,会怎么样呢?借鉴软件领域的发展状况,伯克利研究团队认为,指令集体系结构作为软硬件接口的一种标准,不应该像x86和ARM等指令集那样需要授权才能使用,而应该开放(Open)出来让大家自由(Free)使用,这样才能塑造芯片领域的繁荣生态。

于是,他们启动了一个项目,从零开始设计一款新的指令集,将其命名为RISC-V(读作RISC-Five),并将其彻底开放。伯克利团队希望全世界任何公司、大学、研究机构与个人都可以开发兼容RISC-V指令集的处理器,都可以融入到基于RISC-V构建的软硬件生态系统,而不需要为指令集付一分钱。值得一提的是,RISC-V扮演的角色是指令集标准,就如同TCP/IP定义了网络包的标准、POSIX定义了操作系统的系统调用标准。基于标准可以有开源的实现,也可以有商业版的实现。

第一版RISC-V指令集于2011年发布,经过多年的发展,如今RISC-V社区已经度过了艰难的起步阶段,正进入快速发展期,前景乐观。全世界很多企业选择从ARM转向RISC-V,全球第一大硬盘公司西部数据已经宣布,未来产品将全面使用RISC-V处理器核心,每年将达到10亿颗!

美国的DARPA(美国国防高级研究计划局)也认为,降低芯片设计门槛将会为未来芯片创新创造巨大的机会。因此,DARPA在2017年启动“电子复兴计划”(Electronic Resurgence Initiative),将开源芯片设计作为核心目标之一,每年投入超过2亿美元的经费,研究如何降低芯片设计门槛,先后资助了5个开源硬件项目(PERFECT、CRAFT、SSITH、POSH、IDEA),部分项目明确指明需要基于RISC-V指令集。DARPA认为开源芯片设计将会为2025—2030年的美国,赋予在半导体电子领域更强大的创新能力。

图2 美国的“电子复兴计划”

(图片来源于DAPRA 网站)

除此之外,其他各国政府部门的芯片研究项目也开始选择RISC-V,比如以色列国家创新局(Israel Innovation Authority)也选择基于RISC-V研制为全国企业服务的处理平台。

印度政府更是将RISC-V视为一次发展处理器的机会。他们为处理器战略项目(SHAKTI)资助9000万美元,目标为研制6款基于RISC-V指令集的开源处理器核,涵盖了32位的单核微控制器、64核64位高性能处理器和安全处理器等多个应用领域。2016年1月,印度电子信息技术部又资助了4500万美元,研制一款基于RISC-V指令集的2GHz四核处理器。在印度政府支持的另一个关

于神经形态加速器(neuromorphic accelerator)项目中,也将RISC-V作为计算主核心。过去几年,随着印度政府资助的处理器相关项目都开始向RISC-V靠拢。

纵观国际形势,我们可以发现,当前一些低端芯片已经有比较丰富的开源芯片设计资源。例如,假设使用180nm工艺研制一款芯片,那么EDA工具链可以使用开源的Magic工具包(包含了Xcircuit、IRSIM、NetGen、Qrouter和Qflow),IP模块可以使用兼容WISHBONE的开源模块(OpenCores),180nm的器件库也有多种开源的选择。再加上流片的成本也很便宜,所以综合起来,研制一款180nm的芯片有可能做到只需要几千美元便可以实现,门槛已经很低了。

然而,对于中高端的芯片,还缺乏类似全套的开源芯片设计工具链与器件资源。让我们畅想一下,如果全世界也拥有了价值上百亿美元的开源芯片设计所需的EDA工具链、IP模块、工艺库等,中高端芯片研制成本降低两个数量级,从数千万元降至十万元级别,那么芯片领域的创新将会像今天的互联网那样层出不穷,中国半导体产业卡脖子的问题也将会迎刃而解。

发展生态 中国成立RISC-V联盟

和开源软件对于中国互联网产业的作用类似,开源芯片生态若能形成气候,则会大幅降低芯片创新门槛,将会对中国乃至全世界半导体产业产生深远的、积极的影响。

构建开源芯片生态是伟大的理想,而RISC-V处理器有可能像Linux那样成为开源芯片生态的基石。但是,只有RISC-V又是远远不够,还需要开源的EDA工具链、IP模块、工艺库等协同合作,才能实现真正的开源芯片生态。

这正如今天的开源软件生态除了Linux以外,还包括大量构建于Linux之上的其他开源工具与开源软件,例如GCC、LLVM、MySQL、Apache等。RISC-V还只是星星之火,但却已展露出燎原之潜力。从当前发展势头来看,RISC-V很有可能像Linux那样成为主宰世界的开放指令集标准。

中国的学术界与企业界也已开始积极行动。历经九个月的研讨与筹备,在网信办、工信部、中科院等多个国家部委支持和指导下,计算所联合国内约20家单位组成的中国开放指令生态(RISC-V)联盟(以下简称联盟)于2018年11月8日,在浙江乌镇举行的第五届互联网大会上,正式宣布成立并举行揭牌发布仪式。联盟由倪光南院士任理事长(笔者任秘书长),旨在以RISC-V指令集为抓手,联合学术及产业界推动开源开放指令芯片及生态的健康发展。

图3 中国开放指令生态(RISC-V)联盟成立

为此,联盟制定了一个“三步走”计划,希望用10年左右的时间,到2030年逐步完成开源芯片生态的建立:

第一步,为开源社区提供经过流片验证的高质量开源RISC-V核、IP核及SoC芯片设计方案;

第二步,逐步构建一套基于开源工具链、开源IP、开源工艺库的SoC芯片设计流程,为企业提供商业版工具与IP之外的开源方案;

第三步,迭代优化形成自动化的开源工具,提高设计验证效率,为大批科研机构、中小企业提供定制芯片服务,降低芯片开发门槛。

敏捷开发 开启开源芯片生态大门

在美好的愿景之下,我们也要清醒地认识到开源软件在协作开发、质量控制、商业模式、生态构建等方面都经历了很多次失败的尝试与探索,才沉淀出LAMP/MEAN这样成熟的开源软件组合。

开源芯片生态仍处于襁褓阶段,未来的发展也必然会面临很多挑战。开源芯片最大的挑战之一在于芯片开发门槛高,如果能数量级降低开发门槛(成本与周期),那就可能吸引广大的芯片开发者。芯片敏捷开发,将会是降低芯片开发门槛的关键,将成为开启开源芯片生态的钥匙。

软件开发早已采用敏捷开发模式,通过不断迭代、循序渐进的开发方法快速发布软件产品,将以往数年的开发周期大幅缩减为几个月(如图4左所示)。然而,如今芯片的开发周期仍然需要数年,往往设计和验证工作需要花费1—2年,投片需要花费约1年。如果流片失败,投入的时间和精力将会付之东流,风险非常大。这也导致今天基于这种模式开发的IP模块价格非常高昂,进一步又推高了芯片设计成本。

图4 软硬件协同的敏捷开发模式

开发成本与周期正是芯片设计门槛高的主要原因。因此,芯片敏捷开发有可能撬动上述困境的支点——如果通过敏捷开发模式将芯片设计成本降低到几十万甚至几万、开发周期降低到几个月,那么用这种方式开发的IP模块成本也将大幅下降,开发人员将更愿意开源与共享IP模块。

当芯片开发周期也能从数年缩减为几个月,那将形成一种软硬件协同的敏捷开发模式(如图4所示),这将颠覆现在的IT产品开发模式。如今,互联网应用开发团队一般有负责手

机APP的前端工程师,与负责服务器端的后端工程师配合起来一起开发。而在未来的软硬件协同敏捷开发模式下,开发团队将包括软件端工程师与硬件端工程师——软件端通过几个月开发出新的软件功能,硬件端则用几个月很快实现出相应的加速芯片。这正是两位图灵奖得主John Hennessy与David Patterson在图灵奖演讲中所推崇的领域专用体系结构DSA(Domain-Specific Architecture)的体现。

事实上,在推广RISC-V的同时,伯克利研究团队也开放了RISC-V的SoC实现Rocket Chip以及面向敏捷开发的硬件设计语言Chisel,期望通过“RISC-V+Rocket+Chisel”这三驾马车推动芯片设计领域迈进敏捷开发时代,降低芯片设计门槛。我们团队也在基于新的硬件开发语言Chisel上开展了一系列芯片敏捷开发实践。

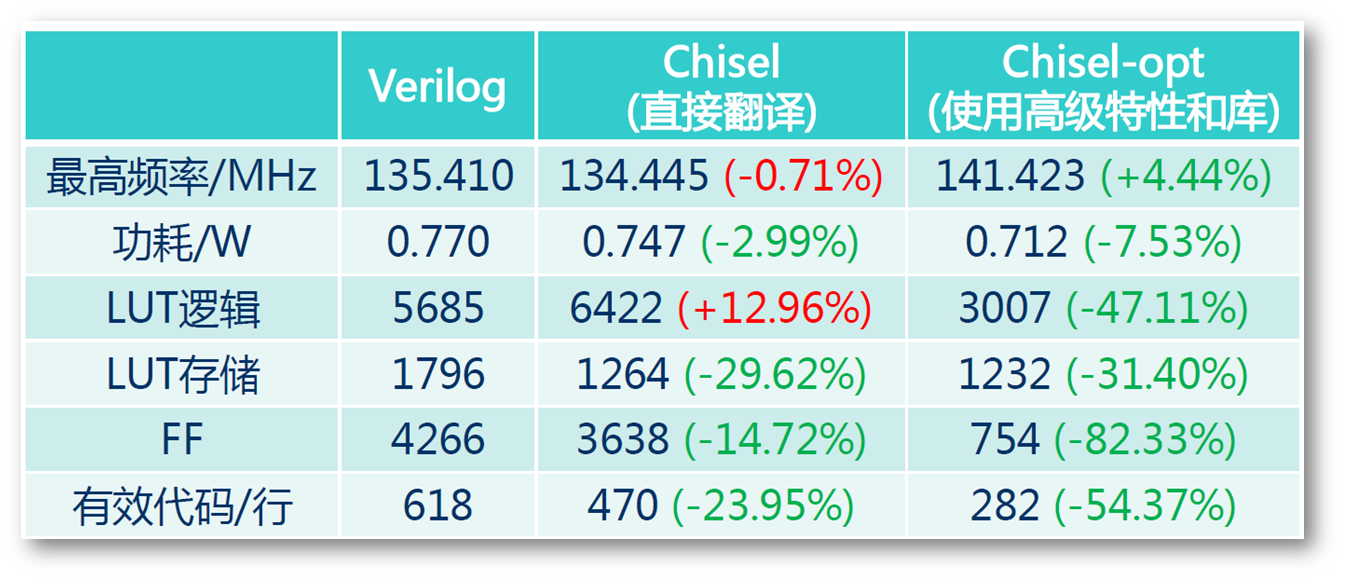

我们团队曾经由于项目需要,期望尽快实现一个简单的共享二级缓存(L2 Cache),集成到标签化RISC-V项目中。团队中的两人分别进行独立开发。一位是团队中的工程师,他在标签化项目的早期阅读并理解过OpenSPARC T1的二级缓存源代码,也修改过赛灵思系统缓存,在其中成功添加基于标签的路划分功能,具体丰富的缓存设计经验。参与开发的另外一位人员是团队中的大四本科实习生,他做过CPU课程设计,并有9个月的Chisel开发经验,但从未设计过二级缓存。这位本科生使用敏捷开发模式, 选择使用Chisel语言来开发这个缓存。如表2所示,在这个案例中,敏捷开发模式的效率是传统开发模式的14倍!

表2 L2 cache 开发案例对比

为了进一步对比Chisel和Verilog的效果,我们找到团队中的另一个没有Chisel开发经验的大四实习本科生,让他来把这位工程师的Verilog代码中的部分关键模块翻译成功能等价的Chisel代码。我们在项目中提供了一些测试,用于证明翻译结果与Verilog实现的功能等价。表3列出了两种语言实现模块的主要性能参数,可以看到一位大四本科生使用Chisel也能产生较高质量的硬件模块实现。

表3 Chisel 和Verilog 的性能、功耗、面积和对比

这个案例很好地展现了一个敏捷开发的例子。一个本科生的Chisel新手,可以在更短的时间内编写更少的代码,代码质量就能达到和工程师相当的水平,甚至还可以超越工程师。即使代码质量与传统开发有20%的差距,敏捷开发仍然展现了其节省人力和时间的价值——能快速构建一个可以工作的原型,对项目开展来说是非常有意义的。从这点来看,敏捷开发确实大大降低了硬件开发的门槛。

作为全世界最大的芯片用户,中国一直希望能把国产芯片产业做大做强,各方也都在努力。借鉴开源软件对于中国互联网发展的作用,也许开源芯片设计是一条值得尝试的道路。在此,呼吁更多的中国企业、工程师与学者投身开源芯片设计行动,携手推动开放指令芯片发展,共创开源芯片生态黄金时代!

致谢:感谢中科院计算所孙凝晖研究员对本文观点的建议与指导,感谢笔者团队成员在芯片敏捷开发方向的投入与付出,感谢《前沿科学》杂志毕文婷女士的编辑校审。

(原文刊载于《前沿科学》2018年第4期,部分图表为网络版替换)

更多资料请参阅:

【1】中国开放指令生态(RISC-V)联盟,“开放指令集与开源芯片发展报告”,2019年1月

http://crva.io/documents/OpenISA-OpenSourceChip-Report-v1p0.pdf

【2】余子濠,刘志刚,李一苇,黄博文,王卅,孙凝晖包云岗,“芯片敏捷开发实践:标签化RISC-V”,计算机研究与发展,2019年1月.

http://acs.ict.ac.cn/baoyg/downloads/Agile-Chip-Design.pdf

https://blog.sciencenet.cn/blog-414166-1163127.html

上一篇:我的2018:微信朋友圈的24个瞬间

下一篇:非“首创”研究等于低价值吗?